在基于GD32系列微控制器的嵌入式系統設計中,晶振電路是確保系統穩定運行的核心。一個設計良好的晶振電路為MCU提供精確的時鐘源,直接影響程序的執行時序、通信接口的波特率精度以及外設模塊的可靠性。本文旨在為電子技術開發者,特別是21ic電子技術開發論壇的工程師們,提供一個清晰、實用的GD32晶振電路設計指南。

1. 晶振電路的基本構成與選擇

GD32 MCU通常支持兩種時鐘源:外部高速晶振和外部低速晶振。

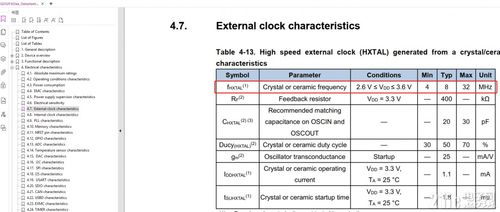

- 外部高速晶振:為主系統提供時鐘,頻率范圍常見為4MHz~32MHz(具體需查閱對應型號的數據手冊)。這是系統運行、外設工作的主要時鐘源。

- 外部低速晶振:通常為32.768kHz,主要用于實時時鐘模塊,提供精確的計時基準。

晶振選擇關鍵參數:

頻率:根據系統需求選擇。8MHz和12MHz是常見選擇,平衡了性能和通用性。

負載電容:這是晶振最重要的參數之一,標注為CL,典型值如12pF, 20pF等。它決定了外部匹配電容的值。

* 精度:根據應用對時鐘精度的要求選擇,如±10ppm、±20ppm等。通信應用(如USB、UART)通常要求更高的精度。

2. 標準電路設計與元器件計算

一個典型的外部高速晶振電路如下圖所示(概念示意):

`

VDD (3.3V)

|

[Rf] (可選,1MΩ典型值)

|

+---- XO (晶振輸出) ----||---- OSC_IN (MCU引腳)

| C1

[晶振] |

| GND

+---- XI (晶振輸入) ----||---- OSC_OUT (MCU引腳)

C2

|

GND`

晶振:核心器件。

負載電容C1, C2:其值由晶振要求的負載電容CL、電路板寄生電容(Cs,通常估算為2~5pF)和MCU引腳輸入電容(Ci,詳見數據手冊)共同決定。計算公式為:

`

C1 = C2 = 2 (CL - Cs) - Ci

`

例如,若晶振CL=20pF,估算Cs=3pF,Ci=5pF,則C1=C2 = 2(20-3)-5 = 29pF。可選擇最接近的標準值,如22pF并聯6.8pF,或直接使用27pF或33pF。這是設計的關鍵步驟。

- 反饋電阻Rf:對于GD32,內部通常已集成,外部可省略。若需要,可并聯一個1MΩ~10MΩ的大電阻,有助于起振穩定。具體請參考對應型號的參考手冊。

- 布局布線要點:

- 最短走線:將晶振、電容盡可能靠近MCU的OSCIN和OSCOUT引腳放置。

- 包圍地線:用接地銅皮包圍整個晶振電路,并與主地平面通過單點連接,以隔離噪聲。

- 遠離噪聲源:遠離高頻信號線、電源開關電路、磁性元件等。

- 避免過孔:連接晶振和電容的走線盡量避免使用過孔。

3. 針對GD32的特殊注意事項

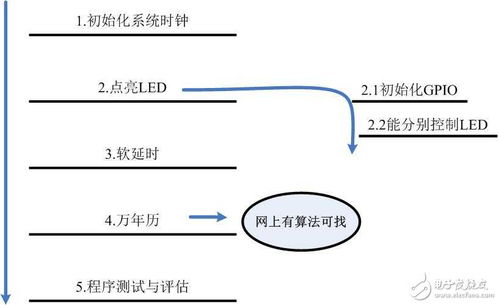

- 啟動配置:GD32的時鐘系統非常靈活。上電后,默認使用內部RC振蕩器。需要在軟件初始化階段,通過配置時鐘樹寄存器,使能并切換至外部高速晶振作為系統時鐘源。務必在代碼中檢查外部晶振是否就緒(通過時鐘控制狀態寄存器)。

- 低功耗模式:在進入某些低功耗模式時,外部高速晶振可能會被關閉以節能。喚醒后,需要根據手冊描述重新使能并等待穩定。

- 硬件設計驗證:

- 最直接的驗證方法是使用示波器探頭(建議使用10X衰減檔,以減小探頭電容影響)測量OSC_IN引腳波形。應觀察到干凈、幅值充足(接近VDD)、頻率準確的正弦波或類正弦波。

- 如果晶振不起振,檢查:電源是否穩定、電容值是否匹配、焊接是否良好、MCU相關引腳配置是否正確(應配置為外部振蕩器模式,而非GPIO)。

- 備選方案:對于時鐘要求不高的應用,GD32的高精度內部RC振蕩器(如8MHz/108MHz等)是可靠且節省成本和PCB空間的方案。但若需USB或高精度定時,外部晶振仍是首選。

4. 外部低速晶振電路

設計原則與高速晶振類似,但因其頻率低、增益小,對負載電容和布局更為敏感。

- 負載電容CL通常為12.5pF。

- 同樣使用兩個匹配電容C1和C2,計算方式相同。

- 走線應更加精簡。

###

設計GD32的晶振電路,關鍵在于:根據數據手冊選擇合適參數的晶振,精確計算并選用匹配的負載電容,以及進行嚴謹的PCB布局布線。遵循以上原則,可以最大程度地保障系統時鐘的穩定與可靠,為整個嵌入式項目的成功奠定堅實基礎。在實際開發中,務必結合具體GD32型號的《數據手冊》和《參考手冊》進行最終設計定稿。